-

首页

-

产品中心

- 光学加工

- 无掩模版紫外光刻机

- 超高精度3D光刻设备

- 光学检测

- 3D显微镜/轮廓仪

- 光电分析设备

- 磁学分析设备

- 加工服务及耗材

- 代加工服务

- 3D光刻材料

- 光刻胶及配套试剂

- 更多产品

- 超低温恒温器

- 激光器

- 光学平台

- 电输运接线盒

- 显微物镜

-

技术百科

-

客户案例

-

新闻中心

-

关于我们

- 公司简介

- 技术支持

- 在线留言

- 联系我们

-

首页

-

产品中心

- 光学加工

- 无掩模版紫外光刻机

- 超高精度3D光刻设备

- 光学检测

- 3D显微镜/轮廓仪

- 光电分析设备

- 磁学分析设备

- 加工服务及耗材

- 代加工服务

- 3D光刻材料

- 光刻胶及配套试剂

- 更多产品

- 超低温恒温器

- 激光器

- 光学平台

- 电输运接线盒

- 显微物镜

-

技术百科

-

客户案例

-

新闻中心

-

关于我们

- 公司简介

- 技术支持

- 在线留言

- 联系我们

客户成果丨华南师范大学《ACS Applied Materials & Interfaces》:用于多级存储和光电子逻辑门的铁电α-In₂Se₃ 半浮栅晶体管

近年来,α-In2Se3等二维铁电材料凭借其独特的铁电极化特性,被广泛应用于铁电浮栅晶体管或铁电场效应晶体管。铁电极化效应使器件能在断电后长期保持存储电荷而不受外界干扰,从而实现长效数据存储,缓解传统冯·诺伊曼架构因频繁数据传输导致的功耗与延迟问题。然而,在单器件中集成非易失性存储与数字逻辑运算等多项功能仍存在挑战,而这正是发展高集成度、低功耗集成电路应用的关键。因此,探索晶体管层面的存算一体化能力,将成为推动集成电路与人工智能发展的突破性方向。

为了突破以上限制,华南师范大学电子科学与工程学院(微电子学院)霍能杰研究员团队提出了一种采用铁电半导体α-In2Se3作为半浮栅层的半浮栅晶体管(SFGT),该器件同时实现了多级存储与逻辑运算功能。在铁电极化场的调控下,相较于无α-In2Se3层的器件,该结构展现出显著增强的非易失性存储性能,包括更高的编程/擦除比和更长的数据保持时间。通过向底部硅基底和石墨烯栅极同步施加电压脉冲,SFGT可在10 mV的低偏压下实现多级存储功能,并执行"与"(AND)、“或非”(NOR)及“或”(OR)逻辑门运算。这种铁电半浮栅架构使该晶体管在处理复杂逻辑运算时,成为人工智能器件集成的理想选择。

本研究成果以“Ferroelectric α‑In2Se3 Semi-floating Gate Transistors for Multilevel Memory and Optoelectronic Logic Gate”为题发表在《ACS Applied Materials & Interfaces》上。

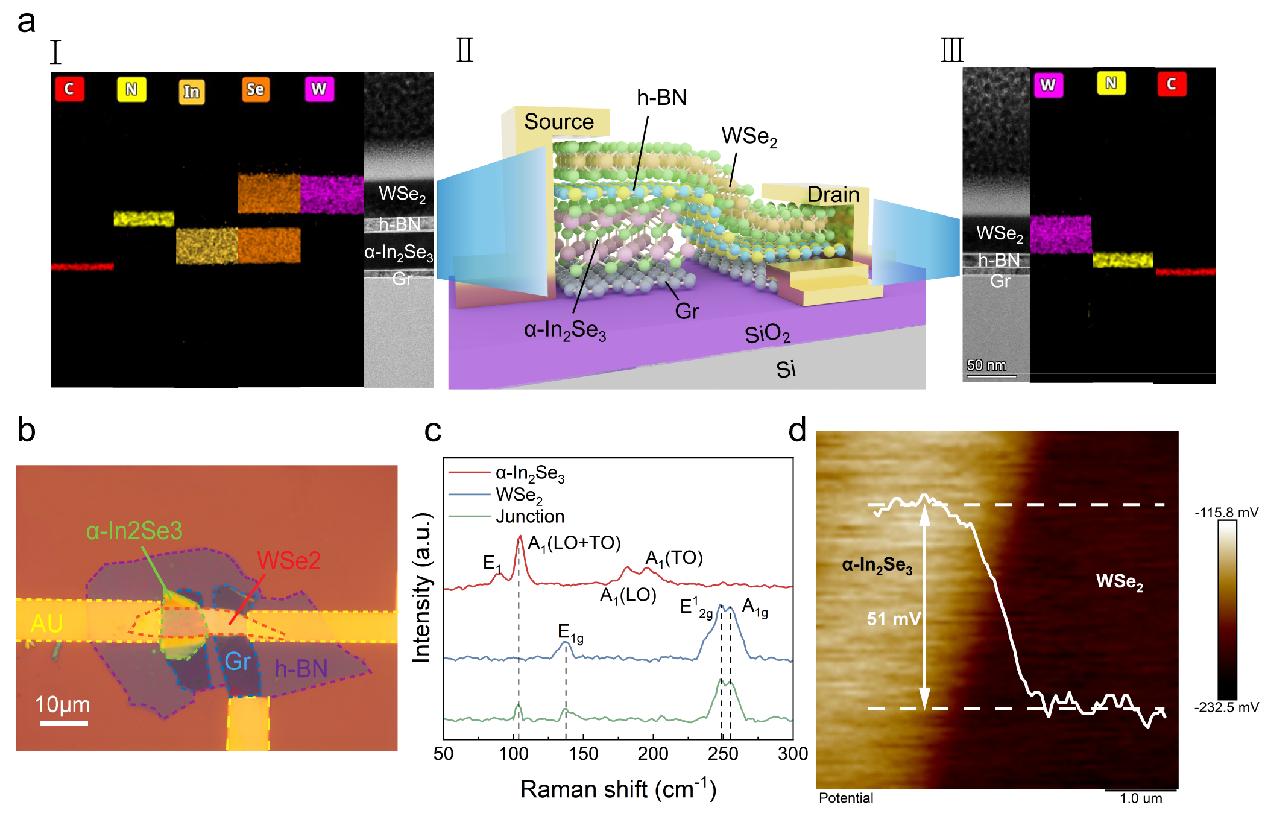

图一:(a) (Ⅱ) 半浮栅晶体管结构示意图及(Ⅰ、Ⅲ) 器件左右两侧的透射电子显微镜(TEM)图像与对应能谱(EDX)元素分布图。(b) 器件光学显微镜(OM)图像。(c) α-In2Se3、WSe2及WSe2/h-BN/α-In2Se3/石墨烯(Gr)范德瓦尔斯异质结的拉曼光谱。(d) WSe2/h-BN/α-In2Se3异质结构的表面电势差分布。

本文器件结构为非对称性的,含有α-In2Se3铁电半浮栅的一侧负责实现非易失性存储功能,另一侧负责实现电导调制功能。透射电子显微镜(TEM)清晰呈现出不同二维材料层间均匀且原子级锐利的界面结构。对应的能谱(EDX)元素分布图同步展示了W、Se、N、In和C的元素分布。通过开尔文探针力显微镜(KPFM)测得WSe2/h-BN/α-In2Se3异质结表面电势差。

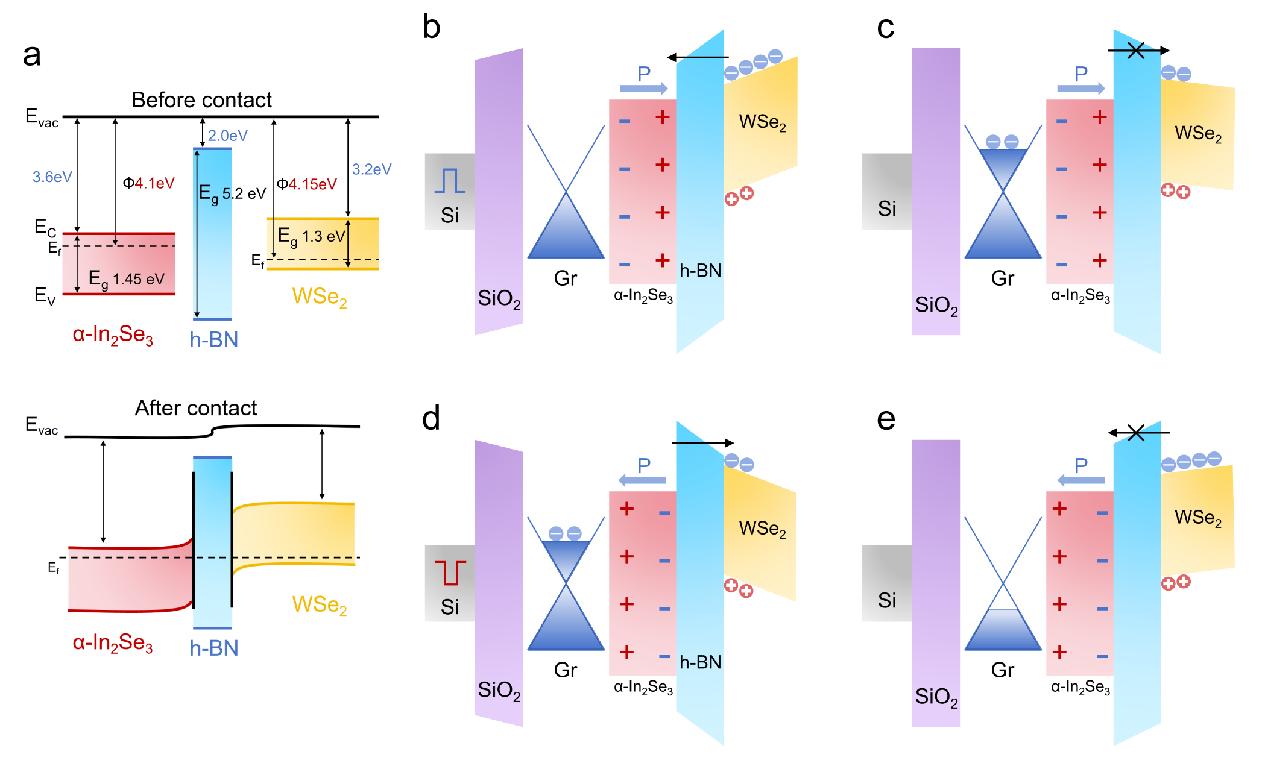

图二:(a) WSe2与α-In2Se3在接触前(上图)及接触后(下图)的能带对齐示意图。半浮栅晶体管在以下工作状态下的能带结构示意图:(b) 编程VSi脉冲施加阶段,(c) 极化电场作用阶段,(d) 擦除VSi脉冲施加阶段,(e) 极化电场作用阶段。

通过能带角度解释α-In2Se3铁电半浮栅晶体管器件存储功能的编程/擦除过程及编程/擦除状态保持实现的原理。

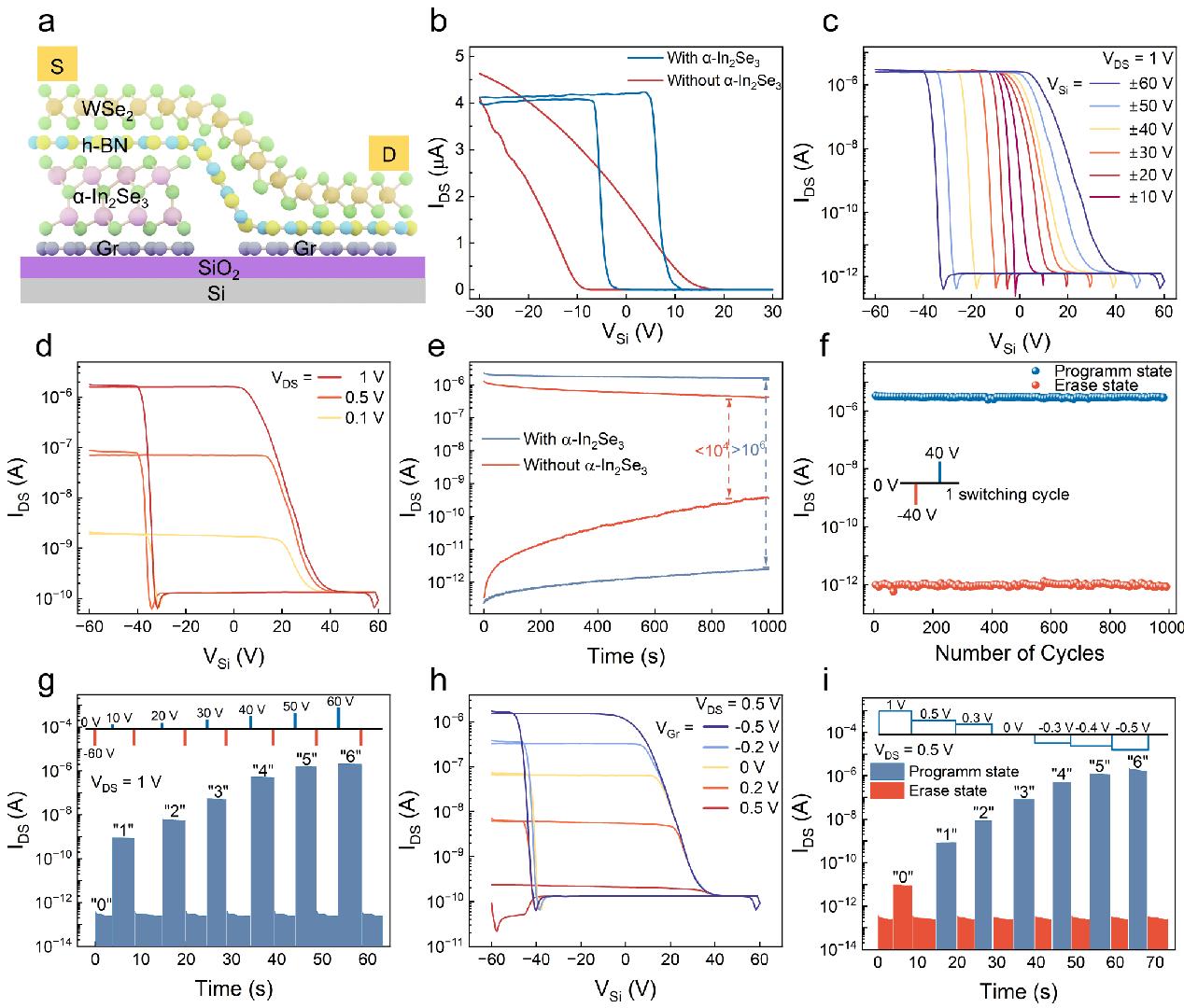

图三:(a) SFGT器件结构示意图。(b) 含α-In2Se3铁电层器件与不含铁电层器件的双向扫描转移特性曲线对比。(c) 不同VSi扫描范围下含α-In2Se3器件的转移特性曲线。(d) 不同VDS偏压下器件的转移特性曲线。(e) 两种器件的保持特性对比。(f) 器件的耐久特性测试(采用±40V脉冲序列进行编程/擦除状态切换)。(g) 通过调节VSi脉冲幅度实现的多级非易失性电流状态调控。(h) 不同石墨烯栅压(VGr)下的器件转移特性曲线。(i) 通过调节VGr幅度实现的多级非易失性电流状态调控。

展示了α-In2Se3铁电半浮栅晶体管器件的电学特性。器件有超过106的编程/擦除(P/E)比和60%的较大存储窗口和两种模式实现的多级存储功能,体现其非易失存储性能优异。有α-In2Se3铁电半浮栅层的器件相对于没有的器件拥有更陡峭的转移曲线和更长时间的数据保持能力,反映出α-In2Se3铁电半浮栅层在存储功能中发挥重要作用。

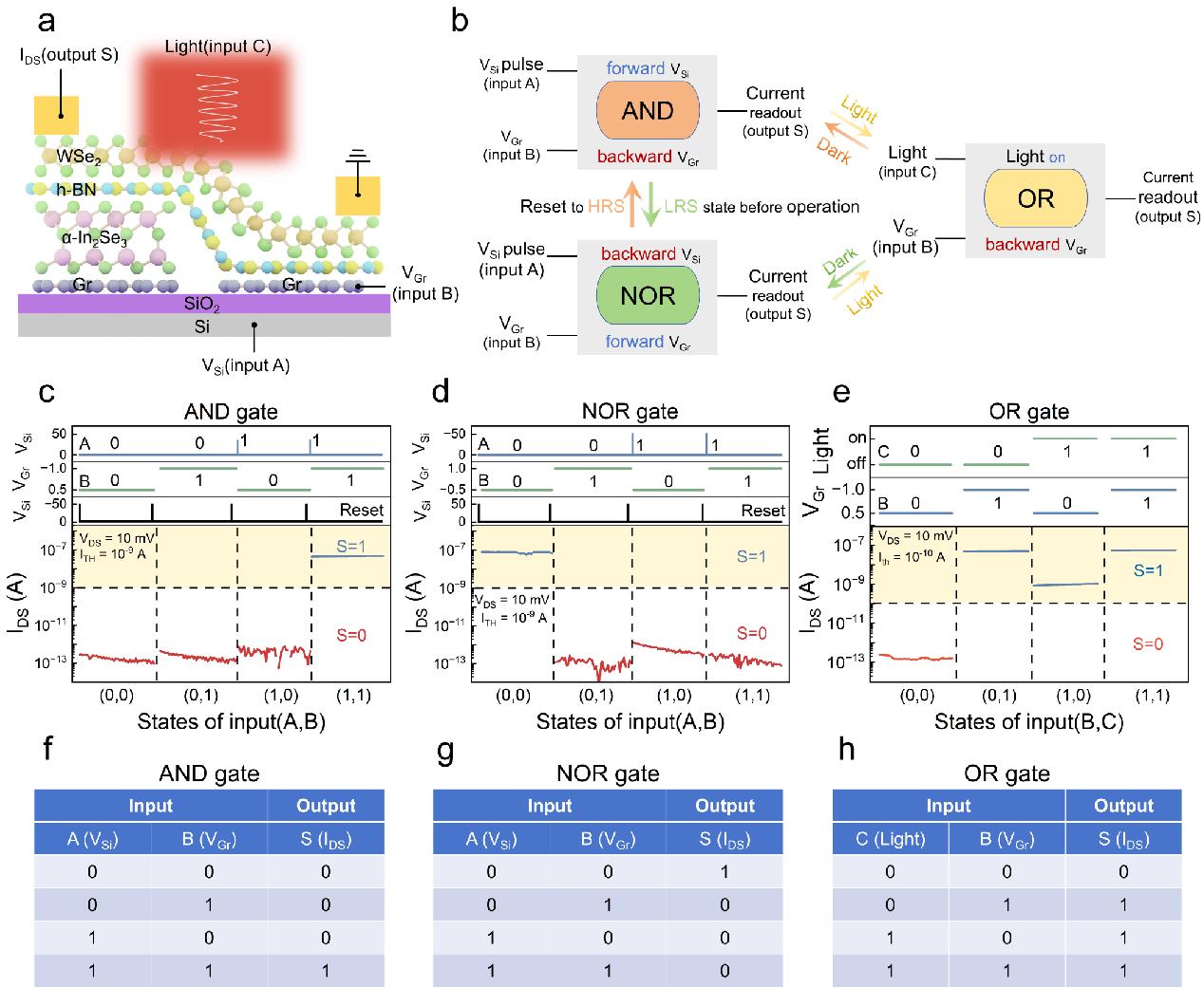

图四:(a) 逻辑门结构示意图。采用VSi脉冲、VGr脉冲和光信号作为逻辑输入(A、B和C),漏源电流作为逻辑输出(S)。(b) 不同逻辑门的工作机制示意图。通过设计的脉冲电压和光调控方案实现:(c) 与门(AND)、(d) 或非门(NOR)和(e) 或门(OR)逻辑功能。(f) 与门、(g) 或非门和(h) 或门逻辑功能的真值表。

展示了以α-In2Se3铁电半浮栅晶体管器件为基础的光电逻辑门的原理及性能。器件将硅栅、石墨烯栅和635 nm波长光作为逻辑输入,以沟道电流水平作为逻辑输出,通过改变实验条件和阈值电流大小,在10 mV的超低工作电压下可实现“与”、“或”和“或非”三种逻辑门功能。

本研究成功开发了一种以铁电半导体α-In2Se3作为半浮栅层的半浮栅晶体管(SFGT),该器件同时实现了多级存储与光电逻辑门功能。得益于α-In2Se3的铁电极化特性,器件展现出显著增强的非易失性存储性能。结合双栅压调控与光信号输入,该器件在10 mV低偏压下即可作为光电逻辑门。与传统浮栅晶体管(FGT)结构相比,这种铁电半浮栅架构为集成化高性能多级非易失性存储器与数字逻辑运算单元提供了创新解决方案。

该工作中通过使用TuoTuo Technology的无掩模光刻机完成了二维铁电α-In2Se3半浮栅晶体管器件的电极图案制备工作。该研究得到了国家自然科学基金、广东基础和应用基础研究基金的资助。

论文链接:

https://doi.org/10.1021/acsami.5c01586