-

首页

-

产品中心

- 光学加工

- 无掩模版紫外光刻机

- 超高精度3D光刻设备

- 光学检测

- 3D显微镜/轮廓仪

- 光电分析设备

- 磁学分析设备

- 加工服务及耗材

- 代加工服务

- 3D光刻材料

- 光刻胶及配套试剂

- 更多产品

- 超低温恒温器

- 激光器

- 光学平台

- 电输运接线盒

- 显微物镜

-

技术百科

-

客户案例

-

新闻中心

-

关于我们

- 公司简介

- 技术支持

- 在线留言

- 联系我们

-

首页

-

产品中心

- 光学加工

- 无掩模版紫外光刻机

- 超高精度3D光刻设备

- 光学检测

- 3D显微镜/轮廓仪

- 光电分析设备

- 磁学分析设备

- 加工服务及耗材

- 代加工服务

- 3D光刻材料

- 光刻胶及配套试剂

- 更多产品

- 超低温恒温器

- 激光器

- 光学平台

- 电输运接线盒

- 显微物镜

-

技术百科

-

客户案例

-

新闻中心

-

关于我们

- 公司简介

- 技术支持

- 在线留言

- 联系我们

客户成果丨华南师范大学《AFM》:基于多区域势垒调制光电晶体管的高运算密度逻辑门多比特算术逻辑单元

边缘计算借助物联网与人工智能技术,通过本地化处理实现实时决策和数据过滤,显著减轻云端负载与带宽压力。在工业与自动驾驶等场景中,依托算术逻辑单元(ALU)进行边缘运算,可提升响应速度并大幅减少数据传输量。然而,当前ALU的数据处理能力依赖于CMOS数字逻辑门与大量晶体管集成,随着电路复杂化,芯片功耗与晶体管数量持续增加,在器件尺寸逼近物理极限的背景下,如何以更少甚至单个器件实现逻辑功能,成为提升FPGA能效与推动边缘计算进一步发展的关键挑战。

针对以上问题华南师范大学电子科学与工程学院(微电子学院)陈洪宇副研究员课题组在新型逻辑架构器件领域中取得最新进展,该研究成果以“High Operation Density Logic-Gates for Multi-Bit Arithmetic Logic Unit Based on Multi-Region Barrier Modulation Optoelectronic Transistor”为题发表在《Advanced Functional Materials》上。该研究通过新型器件架构设计,利用多区域势垒调制的独特优势,将全逻辑门单元晶体管消耗量较传统电路减少90%以上,为新一代算术逻辑单元的发展开辟了新路径。

研究团队提出了一种独特的栅极工程方法,无需任何化学或物理掺杂处理,通过选择不同的区域栅极配置或激光信号作为逻辑输入信号,利用P-MoTe2的双表面通道属性和双向光响应特性,构建了一个高性能的全逻辑门器件。器件所实现的8种基本逻辑门在不同逻辑状态下逻辑“1”与逻辑“0”的比值均超过103。得益于多区域势垒调制的独特能力,该全逻辑门单元晶体管消耗量与CMOS工艺标准相比,逻辑门的晶体管消耗量降低到理论最小值的10%。

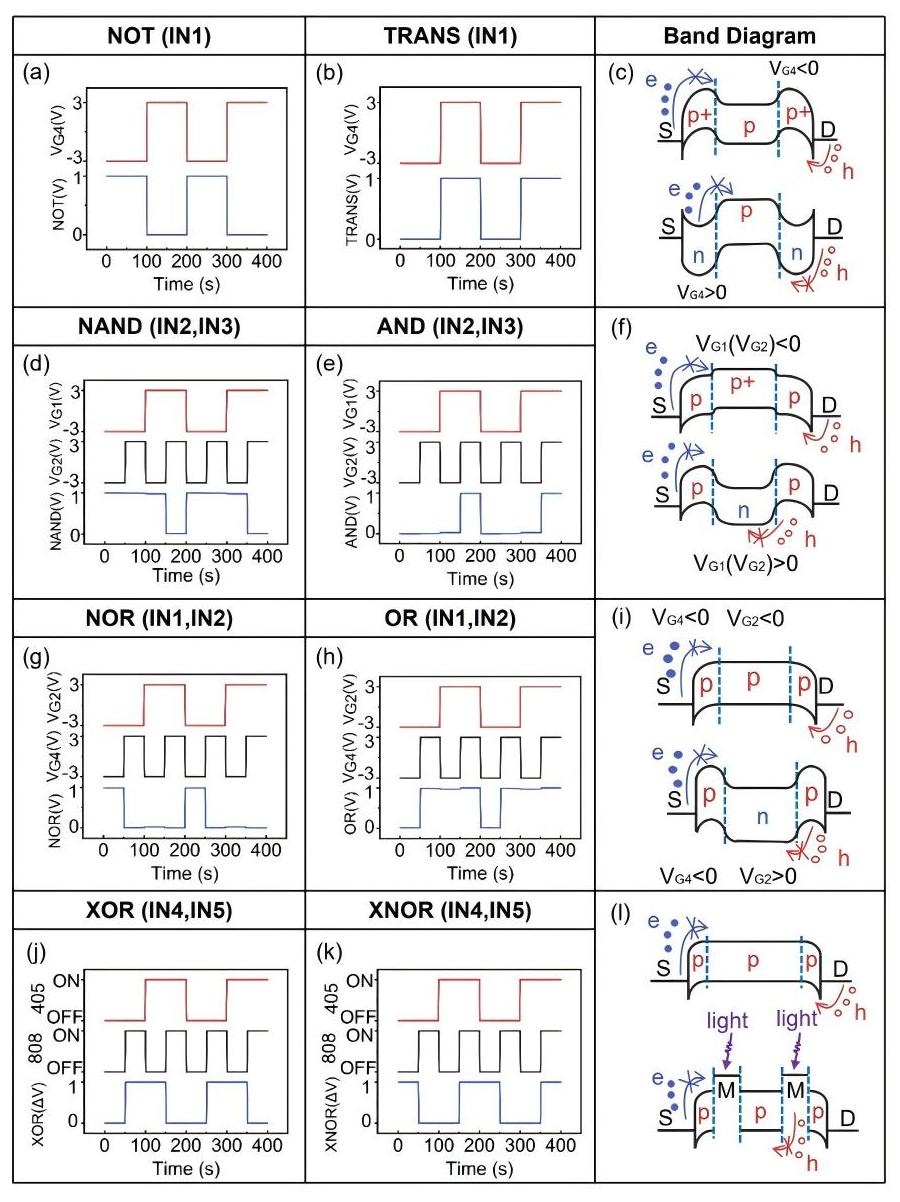

图1 全逻辑门器件逻辑功能的具体实现与控制原理。NOT为仅由VG4调控的单输入单输出逻辑门:(a-c) NOT与TRANS的电压输出曲线及能带示意图。与非门(NAND)为VG1与VG2同步调控的双输入单输出逻辑门:(d-f) NAND与AND的电压输出曲线及能带示意图。NOR为VG2与VG4同步调控的双输入单输出逻辑门:(g-i) NOR与OR的电压输出曲线及能带示意图。XOR为405 nm与808 nm激光信号同步调控的双输入单输出逻辑门:(j-l) XOR与XNOR的电压输出曲线及能带示意图。

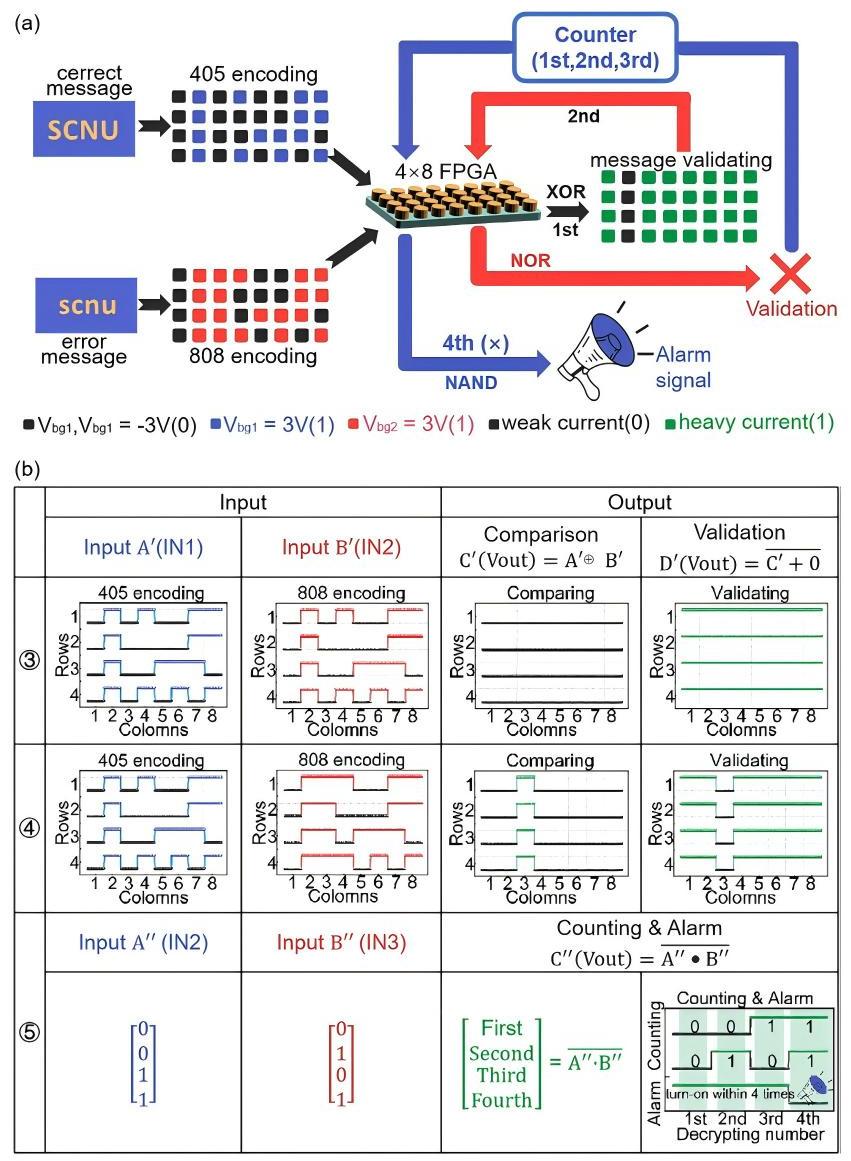

此外,研究基于多区域栅p-MoTe2晶体管设计了4×8 FPGA,构建了一个在多用户之间传递信息的安全通信系统。其中,用户信息以标准ASCII代码为对照,通过编解码过程生成405和808的无符号8位二进制光信息矩阵,再与用户自定义密钥矩阵通过XOR计算进行信息加密与解密。所得信息正确与否通过NOR计算进行验证,验证结果进而通过NAND计算触发警报。以上信息加密/解密和验证报警的信号处理过程都在同一器件单元中完成,同时团队也从通信安全应用方面证明了器件的系统级联可行性。

图2 4×8 FPGA安全通信系统的信息验证与警报流程。(a) 全逻辑门器件阵列的信息验证与警报过程示意图。处于XOR模式的FPGA对解密获得的信息与参考信息进行首次比对验证。验证结果在NOR模式的FPGA中进行二次确认。当验证错误次数超过三次时,编程为NAND模式的FPGA将生成警报信号。(b) 信息验证与警报的矩阵计算过程在FPGA中的实现。流程③展示解密成功时两次验证过程的矩阵信息。流程④呈现解密失败时的矩阵信息。流程⑤为解密错误触发警报信号的执行过程。

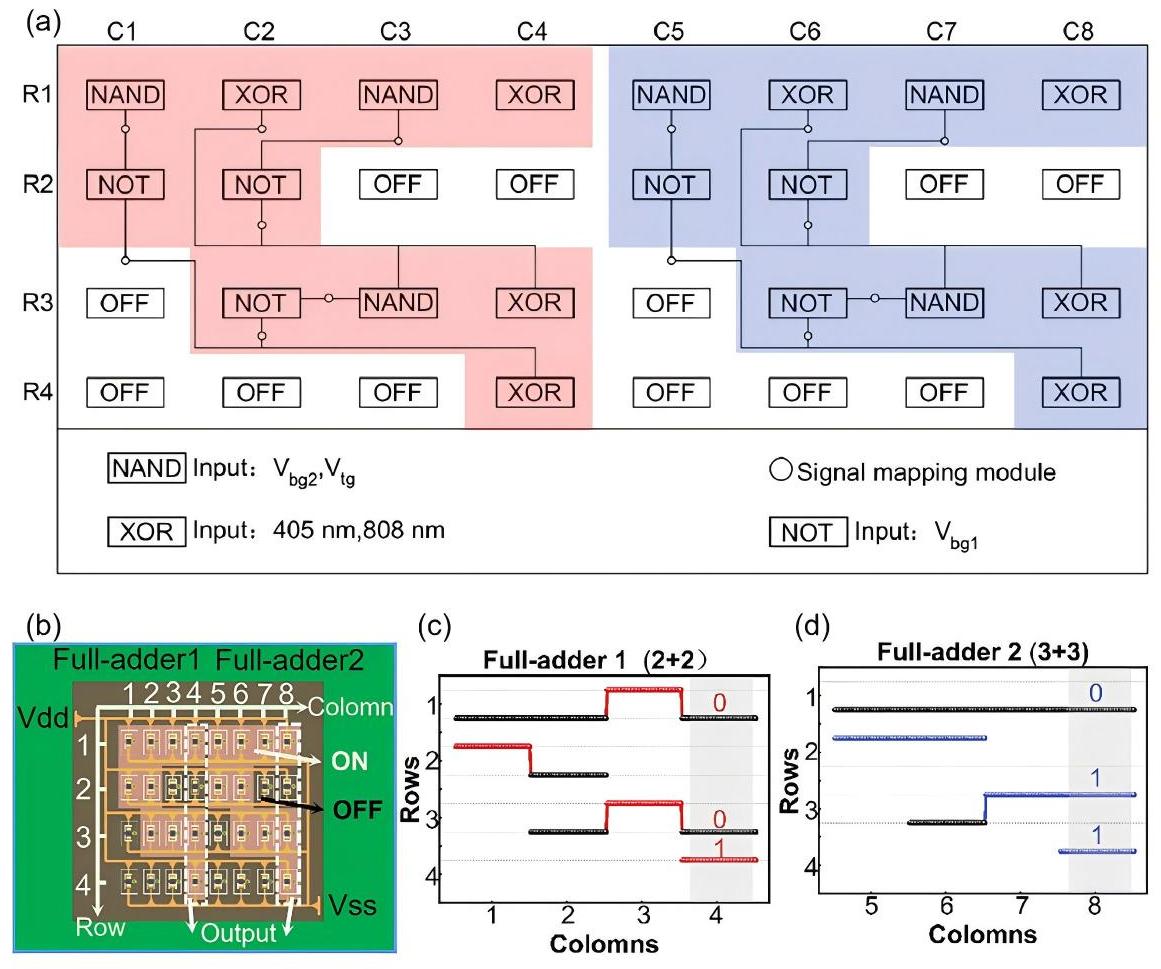

研究进一步在阵列中演示了2个独立工作的2 bit全加法器,在同一模块中完成了算数运算和逻辑运算的统一,极低的晶体管消耗展示了其可作为构建CPU核心的ALU的优越性。团队的器件单元可以制备紧凑、高表现能力、多功能的逻辑门,并在处理数字信号的边缘计算系统级电路上拥有优势。

图3 4×8 FPGA内部两个独立的2位全加器。(a) 在4×8 FPGA中构建两个2位独立全加器的完整逻辑门连接电路。红色与蓝色阴影区域代表处于工作状态用于构建加法器的器件阵列,非阴影区域代表未参与运算的器件。输入信号Vbg2对应VG2,Vtg对应VG1,Vbg1对应VG4。(b) FPGA印刷电路板实物图展示。(c) 全加器1计算(1,1) + (1,1) = (1,1,0)的过程演示。(d) 全加器2计算(1,1) + (1,1) = (1,1,0)的过程演示。

作者信息介绍:华南师范大学电子科学与工程学院(微电子学院)硕士研究生王天生、姬灵萱、王浩为文章的共同第一作者,陈洪宇副研究员为论文的唯一通讯作者。

该工作通过使用TuoTuo Technology(UV Litho-ACA)的无掩模光刻机完成了新型逻辑架构晶体管的接触纯金电极制备工作。此项研究工作获得国家自然科学基金、广东省基础与应用基础研究基金、华南师范大学杰出青年人才项目的持续支持。目前,相关技术已申请发明专利1项。

文章链接:

https://doi.org/10.1002/adfm.202526772